半導体実装技術の進歩により、チップ内に集積化されるトランジスタ数は数十億に達し、さらにアナログ・RF・ディジタル混載のシステム・オン・チップやMEMSなど、LSIの大規模化・多機能化は進展し続けている。また、動作周波数の高速化と製造プロセスの微細化は、寄生容量・抵抗・インダクタンスによる信号配線遅延の影響や製造ばらつきの問題を顕在化させ、トランジスタ・レベルでの物理設計とその解析検証技術の重要性が増大している。本研究室では、半導体チップ・チップを搭載するパッケージ・それらを搭載する高密度実装基板(PCB/PWB)の物理設計を支援するための設計支援ソフトウェアの研究開発を行っている。

キーワード:

- CAD(Computer-Aided Design)/CAE(Computer-Aided Engineering)ソフトウェアの研究

- Electronics Design Automation(電子設計自動化)ソフトウェアの研究開発

- シグナル/パワーインテグリティ検証システムに関する研究

- および上記に関連する要素アルゴリズムに関する研究

半導体パッケージ・高密度実装基板のシミュレーションモデルの作成

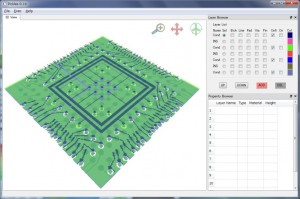

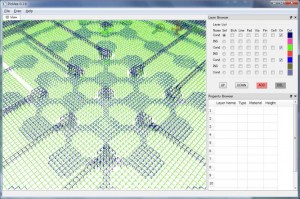

パッケージ・ボードにおける配線を含めた詳細なシミュレーションのためには、対象となる構造物を高精度にモデル化する必要がある。モデル化の方法はシミュレーションの種類により異なり、電磁界シミュレーションを適用する場合は解析領域を有限要素メッシュなどの非構造格子やFDTD法のYeeセルなどの構造格子に分割する必要がある。一方、回路シミュレーションを適用する場合には、対象構造物を等価回路に落とし込む必要がある。本研究では、電磁界シミュレーションと回路シミュレーションの両者について、そのモデル化手法の研究開発を行っている。

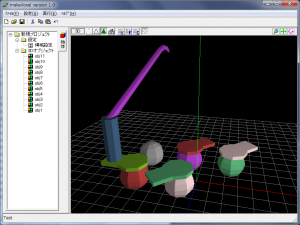

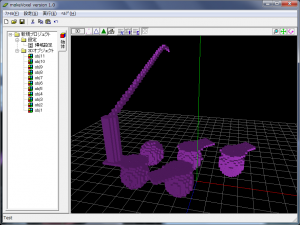

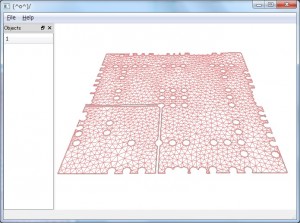

*電磁界シミュレーション向けモデリングツール

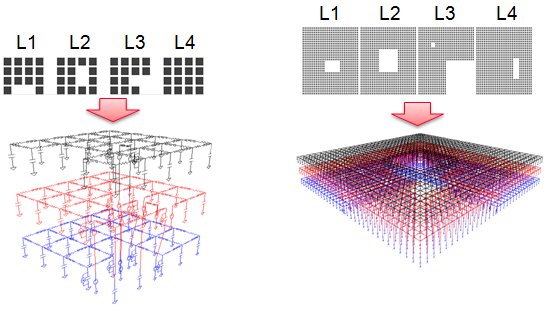

*回路シミュレーション向けモデリングツール

最近の投稿

アーカイブ

- 2025年11月

- 2025年10月

- 2025年9月

- 2025年7月

- 2025年5月

- 2025年3月

- 2025年1月

- 2024年11月

- 2024年9月

- 2024年7月

- 2024年5月

- 2024年3月

- 2024年1月

- 2023年11月

- 2023年10月

- 2023年6月

- 2023年4月

- 2023年2月

- 2023年1月

- 2022年11月

- 2022年9月

- 2022年8月

- 2022年7月

- 2022年3月

- 2022年2月

- 2021年12月

- 2021年11月

- 2021年10月

- 2021年9月

- 2021年4月

- 2020年11月

- 2020年4月

- 2019年12月

- 2019年11月

- 2019年10月

- 2019年9月

- 2019年8月

- 2019年6月

- 2019年5月

- 2019年4月

- 2019年1月

- 2018年12月

- 2018年11月

- 2018年9月

- 2018年8月

- 2018年7月

- 2018年5月

- 2018年3月

- 2018年2月

- 2018年1月

- 2017年12月

- 2017年11月

- 2017年10月

- 2017年9月

- 2017年8月

- 2017年7月

- 2017年5月

- 2017年3月

- 2017年2月

- 2016年11月

- 2016年10月

- 2016年9月

- 2016年8月

- 2016年7月

- 2016年6月

- 2016年3月

- 2015年12月

- 2015年11月

- 2015年9月

- 2015年7月

- 2015年6月

- 2015年5月

- 2015年3月

- 2015年2月

- 2014年12月

- 2014年11月

- 2014年9月

- 2014年8月

- 2014年7月

- 2014年5月

- 2014年3月

- 2014年1月

- 2013年12月

- 2013年8月

- 2013年6月

- 2013年5月

- 2013年3月

- 2012年6月

- 2012年3月

- 2012年2月

- 2012年1月

- 2009年4月